1.集積回路について

1.1 集積回路の概念と誕生

集積回路 (IC): 一連の特定の処理技術を通じて、トランジスタやダイオードなどの能動デバイスと抵抗やコンデンサなどの受動コンポーネントを組み合わせたデバイスを指します。

特定の回路相互接続に従って半導体(シリコンやガリウム砒素などの化合物など)ウェハ上に「統合」され、特定の機能を実行するためにシェルにパッケージ化された回路またはシステム。

1958 年、テキサス インスツルメンツ (TI) で電子機器の小型化を担当していたジャック キルビーは、集積回路のアイデアを提案しました。

「コンデンサー、抵抗器、トランジスターなどのすべてのコンポーネントは 1 つの材料から作成できるため、それらを 1 つの半導体材料上に作成し、それらを相互接続して完全な回路を形成することが可能だと考えました。」

1958 年 9 月 12 日と 9 月 19 日に、キルビーは位相シフト発振器とトリガーの製造とデモンストレーションをそれぞれ完了し、集積回路の誕生を告げました。

2000 年、キルビーはノーベル物理学賞を受賞しました。ノーベル賞委員会はかつてキルビーが「現代の情報技術の基礎を築いた」とコメントした。

下の写真は、キルビーと彼の集積回路特許を示しています。

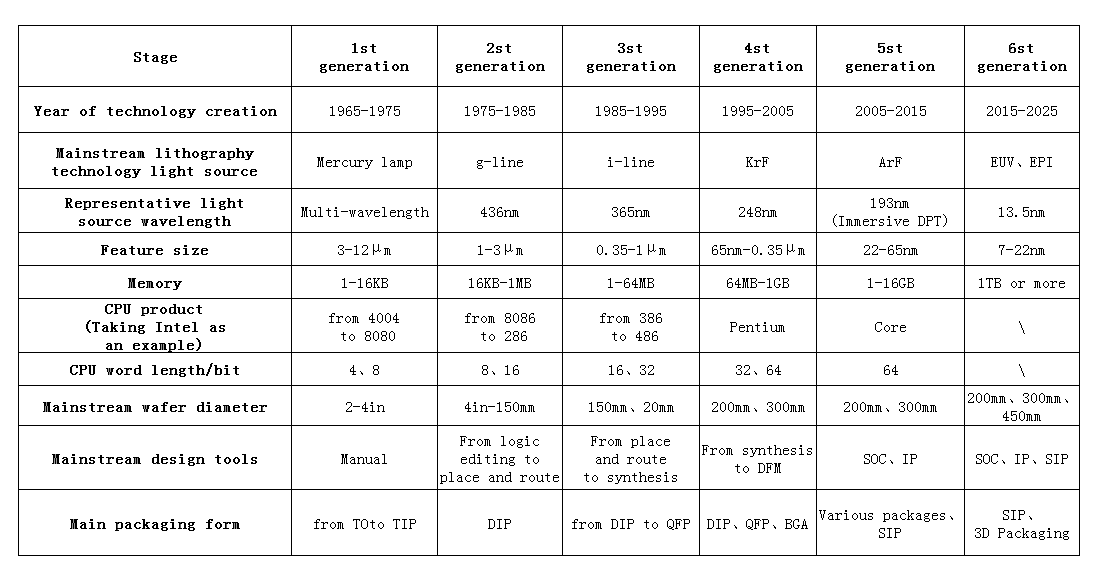

1.2 半導体製造技術の発展

1.3 集積回路産業チェーン

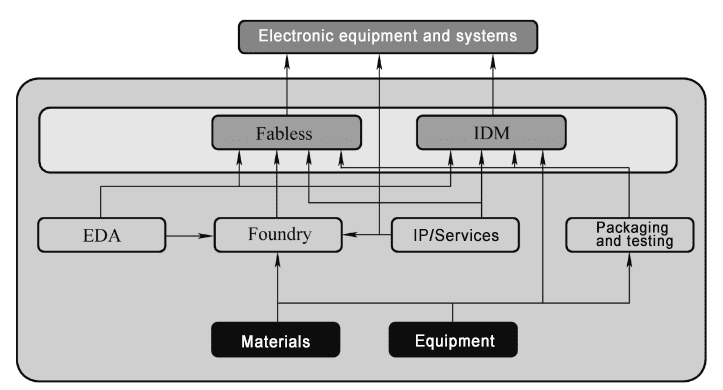

半導体産業チェーン (主にディスクリートデバイスを含む集積回路) の構成を上の図に示します。

・ファブレス:生産ラインを持たずに製品設計を行う企業。

- IDM: 統合デバイス製造業者、統合デバイス製造業者。

- IP: 回路モジュールのメーカー。

- EDA: Electronic Design Automatic、電子設計自動化、主に設計ツールを提供する会社です。

- 鋳造所;チップ製造サービスを提供するウェーハファウンドリ。

- パッケージングおよびテストのファウンドリ会社: 主にファブレスと IDM にサービスを提供します。

- 材料および特殊装置会社:主にチップ製造会社に必要な材料および装置を提供します。

半導体技術を利用して製造される主な製品は、集積回路と個別半導体デバイスです。

集積回路の主な製品には次のものがあります。

- 特定用途向け標準部品 (ASSP);

- マイクロプロセッサユニット (MPU);

- メモリ

- 特定用途向け集積回路 (ASIC);

- アナログ回路;

・一般的な論理回路(Logical Circuit)。

半導体ディスクリートデバイスの主な製品は以下のとおりです。:

- ダイオード;

- トランジスタ;

- パワーデバイス;

- 高電圧デバイス;

- マイクロ波装置;

- オプトエレクトロニクス;

- センサーデバイス(センサー)。

2. 集積回路の製造プロセス

2.1 チップの製造

数十、さらには数万の特定のチップをシリコン ウェーハ上に同時に作成できます。シリコンウェーハ上のチップの数は、製品の種類と各チップのサイズによって異なります。

シリコンウェーハは通常基板と呼ばれます。シリコンウェーハの直径は年々大径化が進み、当初は1インチ未満であったものが、現在では一般的に使用されている12インチ(約300mm)、そして14インチ、15インチへと移行しつつあります。

チップの製造は一般に、シリコンウェーハの準備、シリコンウェーハの製造、チップのテスト/ピッキング、組み立てとパッケージング、最終テストの 5 つの段階に分かれています。

(1)

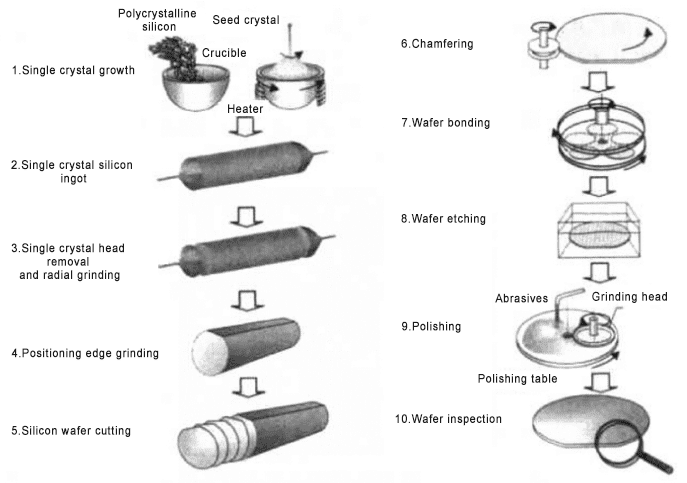

シリコンウェーハの準備:

原料を作るには、砂からシリコンを抽出し、精製します。特別なプロセスにより、適切な直径のシリコンインゴットが製造されます。次に、インゴットはマイクロチップを製造するために薄いシリコンウェーハに切断されます。

ウェーハは、レジストレーションエッジ要件や汚染レベルなどの特定の仕様に合わせて準備されます。

(2)シリコンウェーハの製造:

チップ製造としても知られるベア シリコン ウェーハは、シリコン ウェーハ製造工場に到着し、さまざまな洗浄、膜形成、フォトリソグラフィ、エッチング、ドーピングのステップを経ます。処理されたシリコン ウェーハには、シリコン ウェーハ上に永久的にエッチングされた集積回路の完全なセットが含まれています。

(3)シリコンウェーハの検査と選択:

シリコン ウェーハの製造が完了すると、シリコン ウェーハはテスト/選別エリアに送られ、そこで個々のチップがプローブされ、電気的にテストされます。その後、合格チップと不合格チップが選別され、不良チップにはマークが付けられます。

(4)組み立てと梱包:

ウェーハのテスト/選別後、ウェーハは組み立ておよびパッケージングのステップに入り、個々のチップを保護チューブ パッケージにパッケージ化します。ウェーハの裏面を研削して基板の厚さを減らします。

厚いプラスチックフィルムが各ウェーハの裏面に貼り付けられ、ダイヤモンドチップの鋸刃を使用して、表面のスクライブラインに沿って各ウェーハ上のチップが分離されます。

シリコンウェハの裏面にあるプラスチックフィルムがシリコンチップの脱落を防ぎます。組立工場では、良品チップがプレスまたは真空排気されて組立パッケージが形成されます。その後、チップはプラスチックまたはセラミックのシェルに封止されます。

(5)最終テスト:

チップの機能を保証するために、パッケージ化された各集積回路は、メーカーの電気的および環境特性パラメータ要件を満たすようにテストされます。最終テストの後、チップは顧客に送られ、専用の場所で組み立てられます。

2.2 プロセス部門

集積回路の製造プロセスは一般に次のように分類されます。

フロントエンド: フロントエンドプロセスとは、一般にトランジスタなどのデバイスの製造プロセスを指し、主に素子分離、ゲート構造、ソースとドレイン、コンタクトホールなどの形成プロセスが含まれます。

バックエンド: バックエンドプロセスとは、主にチップ上のさまざまなデバイスに電気信号を伝送できる配線の形成を指し、主に配線間の誘電体蒸着、金属配線の形成、リードパッドの形成などのプロセスが含まれます。

中盤: トランジスタの性能を向上させるために、45nm/28nm 以降の先端技術ノードでは、High-k ゲート誘電体とメタルゲートプロセスが使用され、トランジスタのソースとドレイン構造が準備された後に置換ゲートプロセスとローカル相互接続プロセスが追加されます。これらの工程は前工程と後工程の間にあり、従来の工程では使用されないため中段工程と呼ばれます。

通常、コンタクトホールの準備工程が前工程と後工程の分かれ目となります。

コンタクトホール:第1層金属配線と基板デバイスとを接続するためにシリコンウェハに垂直にエッチングされた穴。タングステンなどの金属が充填されており、素子電極を金属配線層に引き込むために使用されます。

スルーホール: これは、金属相互接続線の 2 つの隣接する層の間の接続パスであり、2 つの金属層間の誘電体層に位置し、通常は銅などの金属で充填されます。

広い意味では:

フロントエンドプロセス: 広い意味では、集積回路の製造にはテスト、パッケージング、その他のステップも含まれる必要があります。テストやパッケージングと比較すると、コンポーネントと相互接続の製造は集積回路製造の最初の部分であり、まとめてフロントエンドプロセスと呼ばれます。

バックエンドプロセス: テストとパッケージ化はバックエンドプロセスと呼ばれます。

3. 付録

SMIF:標準メカニカルインターフェース

AMHS:自動マテリアルハンドリングシステム

OHT:オーバーヘッドホイストトランスファー

FOUP:前開き一体型ポッド、12インチ(300mm)ウェーハ専用

さらに重要なことは、セミセラが提供できるのはグラファイト部品、柔らかい/硬いフェルト、炭化ケイ素部品, CVD炭化ケイ素部品、 そしてSiC/TaC コーティング部品半導体プロセス全体を 30 日で完了します。私たちは、お客様の中国における長期的なパートナーとなることを心から楽しみにしています。

投稿日時: 2024 年 8 月 15 日