半導体産業チェーン、特に第 3 世代半導体 (ワイドバンドギャップ半導体) 産業チェーンには、基板とエピタキシャル層。の重要性は何ですかエピタキシャル層?下地と下地の違いは何ですか?

基板は、ウエハース半導体単結晶材料で作られています。基材が直接内部に侵入する可能性があります。ウエハース半導体デバイスを製造するための製造リンク、または次の方法で処理できます。エピタキシャルエピタキシャルウェーハを製造する工程です。基板は底面ですウエハース(ウェハーをカットすると、ダイを次々と取り出し、それをパッケージ化して伝説のチップにすることができます) (実際、チップの底部は通常、「グランド」接続として使用される裏面の金の層でメッキされています。後工程で作られます)と、全体のサポート機能を担う基盤(チップ内の超高層ビルは基板上に構築されます)。

エピタキシーとは、切断、研削、研磨などによって慎重に加工された単結晶基板上に新しい単結晶を成長させるプロセスを指します。新しい単結晶は基板と同じ材料であっても、異なる材料であってもよい(ホモエピタキシャルまたはヘテロエピタキシャル)。

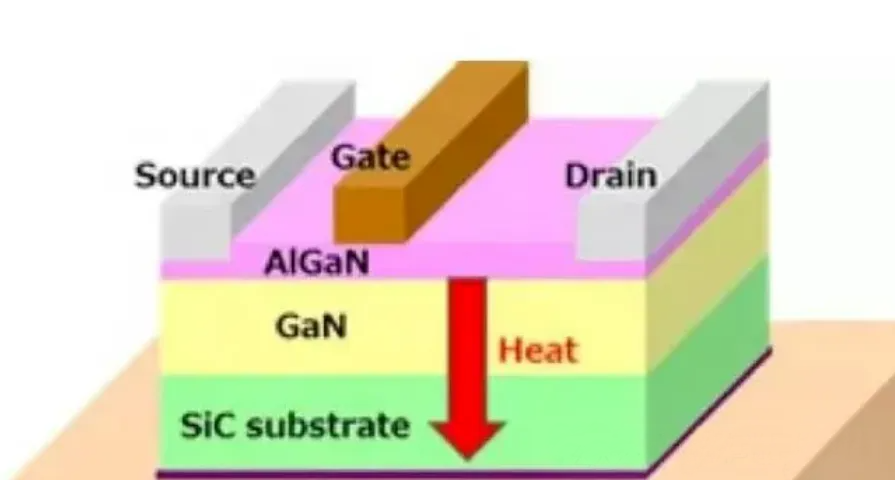

新しく形成された単結晶層は基板の結晶相に沿って成長するため、エピタキシャル層(通常は数ミクロンの厚さ)と呼ばれます。シリコンを例に挙げます。シリコンエピタキシャル成長の意味は、格子構造の整合性が良好な結晶層を成長させることです。ある結晶方位を持ち、基板と比抵抗や厚さが異なるシリコン単結晶基板上にエピタキシャル層を形成した基板をエピタキシャルウェーハ(エピタキシャルウェーハ=エピタキシャル層+基板)と呼びます。デバイスの製造はエピタキシャル層上で行われます。

エピタキシャル性は、ホモエピタキシャル性とヘテロエピタキシャル性とに分けられる。ホモエピタキシャルとは、基板上に基板と同じ材料のエピタキシャル層を成長させることである。ホモエピタキシャル性の重要性は何ですか? – 製品の安定性と信頼性を向上させます。ホモエピタキシャルとは、基板と同じ材料のエピタキシャル層を成長させることですが、材料純度やウェーハ面内均一性を向上させることができます。エピタキシャル加工により加工された基板は、機械研磨により加工された研磨ウェーハと比較して、表面の平坦度が高く、清浄度が高く、微小欠陥や表面不純物が少ない。したがって、抵抗率がより均一になり、表面粒子、積層欠陥、転位などの表面欠陥を制御しやすくなります。エピタキシーは製品の性能を向上させるだけでなく、製品の安定性と信頼性も保証します。

シリコンウェーハ基板上にシリコン原子の別の層をエピタキシャル成長させる利点は何ですか? CMOS シリコンプロセスでは、ウェーハ基板上のエピタキシャル成長 (EPI、エピタキシャル) が非常に重要なプロセスステップです。

1. 結晶品質の向上

基板の初期欠陥と不純物: ウェーハ基板には、製造プロセス中に特定の欠陥や不純物が含まれる場合があります。エピタキシャル層の成長により、基板上に高品質、低欠陥、不純物濃度の単結晶シリコン層が生成されます。これはその後のデバイス製造にとって非常に重要です。均一な結晶構造: エピタキシャル成長により、より均一な結晶構造が確保され、基板材料の粒界や欠陥の影響が軽減され、ウェーハ全体の結晶品質が向上します。

2. 電気的性能の向上

デバイス特性の最適化: 基板上にエピタキシャル層を成長させることにより、シリコンのドーピング濃度と種類を正確に制御してデバイスの電気的性能を最適化できます。たとえば、エピタキシャル層のドーピングにより、MOSFET のしきい値電圧やその他の電気パラメータを正確に調整できます。リーク電流の低減: 高品質のエピタキシャル層は欠陥密度が低いため、デバイス内のリーク電流が低減され、デバイスの性能と信頼性が向上します。

3. 高度なプロセスノードのサポート

フィーチャ サイズの縮小: より小さなプロセス ノード (7nm、5nm など) では、デバイスのフィーチャ サイズは縮小し続けており、より洗練された高品質の材料が必要になります。エピタキシャル成長技術はこれらの要件を満たし、高性能かつ高密度の集積回路製造をサポートします。降伏電圧の向上: エピタキシャル層は、高出力および高電圧デバイスの製造に不可欠な、より高い降伏電圧を持つように設計できます。たとえば、パワーデバイスでは、エピタキシャル層によってデバイスの降伏電圧が向上し、安全な動作範囲が広がります。

4. プロセス互換性と多層構造

多層構造: エピタキシャル成長技術により、基板上に多層構造を成長させることができ、層ごとに異なるドーピング濃度と種類を持たせることができます。これは、複雑な CMOS デバイスの製造や 3 次元の統合の実現に非常に役立ちます。互換性: エピタキシャル成長プロセスは既存の CMOS 製造プロセスと高い互換性があり、プロセス ラインを大幅に変更することなく既存の製造プロセスに簡単に統合できます。

投稿日時: 2024 年 7 月 16 日